开关电源闭环计划从回响基本概念中知道:扩大器在深度负回响时,如输入不变,电路参数改动、负载改动或干扰对输出影响减小。回响越深,干扰引起的输出过错越小。但是,深回响时,回响环路在某一频率附加相位移如到达180°,一起输出信号等于输入信号,就会发生自激振动。开关开关电源不同于一般扩大器,扩大器加负回响是为了有满意的通频带,满意的安稳增益,削减干扰和削减线性和非线性失真。而开关开关电源,假定要等效为扩大器的话,输入信号是基准(参阅)电压Uref,一般说来,基准电压是不变的;回响网络就是取样电路,一般是一个分压器,当输出电压和基准一守时,取样电路分压比(kv)也是固定的(Uo=kvUref)。开关开关电源不同于扩大器,内部(开关频率)和外部干扰(输入开关电源和负载改动)十分严重,闭环计划目的不只需求对以上的内部和外部干扰有很强抑制才能,确保静态精度,而且要有杰出的动态照顾。关于恒压输出开关开关电源,就其回响拓扑而言,输入信号(基准)相当于扩大器的输入电压,分压器是回响网络,这就是一个电压串联负回响。假定恒流输出,就是电流串联负回响。假定是恒压输出,对电压取样,闭环安稳输出电压。因而,首先选择安稳的参阅电压,通常为5~6V或2.5V,要求极小的动态电阻和温度漂移。其次要求开环增益高,使得回响为深度回响,输出电压才不受开关电源电压和负载(干扰)影响和对开关频率纹波抑制。一般功率电路、滤波和PWM发生电路增益低,只需选用运放(过错扩大器)来获得高增益。再有,由于输出滤波器有两个极点,最大相移180°,假定直接参与运放组成回响,很简单自激振动,因而需求相位补偿。根据不同的电路条件,能够选用Venable三种补偿扩大器。补偿结果既满意稳态要求,又要获得杰出的瞬态照顾,一起能够抑制低频纹波和对高频重量衰减。

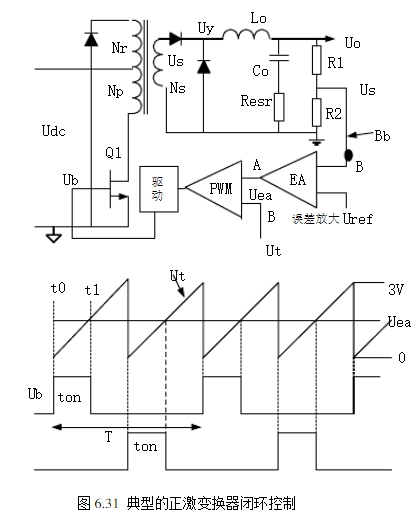

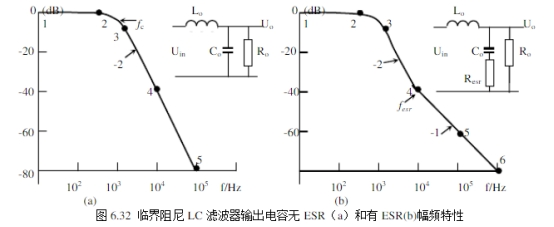

6.4.1 概述图6.31为一个典型的正激变换器闭环调度的比如。能够看出是一个负回响系统。PWM操控芯片中包含了过错扩大器和PWM构成电路。操控芯片也供给许多其他的功能,但了解闭环安稳性问题,仅需考虑过错扩大器和PWM。关于输出电压Uo缓慢或直流改动,闭环当然是安稳的。例如输入电网或负载改动(干扰),引起Uo的改动,经R1和R2取样(回响网络),送到过错扩大器EA的反相输入端,再与加在EA同相输入端的参阅电压(输入电压)Uref比较。将引起EA的输出直流电平Uea改动,再送入到脉冲宽度调制器PWM的输入端A。在PWM中,直流电平Uea与输入B端0~3V三角波Ut比较,发生一个矩形脉冲输出,其宽度ton等于三角波初步时刻t0到PWM输入B三角波与直流电平相交时刻t1。此脉冲宽度选择了芯片中输出晶体管导通时刻,一起也选择了操控晶体管Q1的导通时刻。Udc的添加引起Uy的添加,因Uo=Uyton/T,Uo也随之添加。Uo添加引起Us添加,并因而Uea的削减。从三角波初步到t1的ton相应削减,Uo恢复到它的初始值。当然,反之亦然。PWM发生的信号能够从芯片的输出晶体管发射极或集电极输出,经电流扩大供给Q1基极驱动。但不论从那一点-发射极仍是集电极-输出,有必要确保当Uo添加,要引起ton削减,即负回响。应当注意,大多数PWM芯片的输出晶体管导通时刻是t0到t1。关于这样的芯片,Us送到EA的反相输入端,PWM信号假定驱动功率NPN晶体管基极(N沟道MOSFET的栅极),则芯片输出晶体管应由发射极输出。但是,在某些PWM芯片(TL494)中,它们的导通时刻是三角波Ut与直流电平(Uea)相交时刻到三角波中止时刻t2。关于这样的芯片,假设驱动NPN晶体管,输出晶体管导通(假设从芯片的输出晶体管发射极输出),这样会随晶体管导通时刻添加,使得Uo添加,这是正回响,而不是负回响。因而,TL494一类芯片,Us送到EA的同相输入端,Uo添加使得导通时刻削减,就能够选用芯片的输出晶体管的发射极驱动。 图6.31电路是负回响且低频安稳。但在环路内,存在低电平噪音电压和含有丰盛连续频谱的瞬态电压。这些重量经过输出Lo,Co滤波器、过错扩大器和Uea到Uy的PWM调节器引起增益改动和相移。在谐波重量中的一个重量,增益和相移或许导致正回响,而不再是负回响,在6.2.7节我们已议论过闭环振动的机理。以下就开关开关电源作加体分析。 6.4.2 环路增益 仍是来研讨图6.31正激变换器。假定回响环在B点-连接到过错扩大器的反相输入端断开成开环。任何一次谐波重量的噪声从B经过EA扩大到Uea,由Uea传递到电压Uy的平均值,和从Uy的平均值经过Lo,Co回来到Bb(正好是从前环路断开点)都有增益变化和相移。这便是6.2.7议论的环路增益信号通路。 假设假定某个频率f1的信号在B注入到环路中,回到B的信号的幅值和相位被上面提到回路中的元件改动了。假设改动后的回来的信号与注入的信号相位准确相同,而且幅值等于注入信号,即满意GH=-1。要是现在将环闭合(B连接到Bb),而且注入信号移开,电路将以频率f1继续振动。这个引起开端振动的f1是噪声频谱中的一个重量。 为抵达输出电压(或电流)的静态精度,过错扩大器必须有高增益。高增益就或许引起振动。过错扩大器以外的传递函数一般无法改动,为避免参与过错扩大器往后振动,一般经过改动过错扩大器的频率特性(校正网络),使得环路频率特性以-20dB/dec穿越,并有45°相位裕度,以抵达闭环的安稳。以下我们研讨过错扩大器以外的电路传递函数的频率特性。带有LC滤波电路的环路增益Gf 除了反激变换器(输出滤波仅为输出电容)外,这儿议论的全部拓扑都有输出滤波器。一般滤波器设计时根据脉动电流为平均值(输出电流)的20%选取滤波电感。根据容许输出电压纹波和脉动电流值以及电容的ESR选取输出滤波电容。假设电解电容没有ESR(最新产品),只按脉动电流和容许纹波电压选取。由此取得输出滤波器的谐振频率,特征阻抗,ESR零点频率。在频率特性一节图6.7示出了LC滤波器在不同负载下的幅频和相频特性。 为简化议论,假定滤波器为临界阻尼Ro=1.0Zo,带有负载电阻的输出LC滤波器的幅频特性如图6.32(a)中12345所示。此特性假定输出电容的ESR为零。在低频时,Xc>>XL,输入信号不衰减,增益为1即0dB。在f0以上,每十倍频Co阻抗以20dB削减,而Lo阻抗以20dB添加,使得增益变化斜率为-40dB/dec。当然在f0增益不是遽然转变为-2斜率的。实际上在f0前增益曲线滑润脱离0dB曲线,并在f0后不久渐近趋向-40dB/dec斜率。这儿为议论方便,增益曲线遽然转向-40dB/dec。 假设使相应于Ro=1.0Zo条件下安稳,那么在其它负载也将安稳。但应研讨电路在轻载(Ro>>1.0Zo)时的特性,因为在LC滤波器转机频率f= f0增益谐振提高。

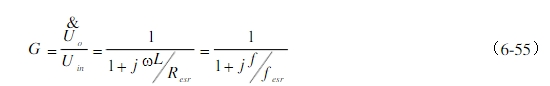

滤波电容有ESR的LC滤波器幅频特性如图6.35b的曲线123456。大多数滤波电容具有ESR。在f0以上的低频段,容抗远远大于ESR,从Uo看到阻抗仅是容抗起首要作用,斜率仍为-40dB/dec;在更高频时,esrRC<<ω1,从输出端看的阻抗仅仅ESR,在此频率规模,电路变为LR滤波,而不是LC滤波。即

式中转机频率fesr=Resr/(2πL)。在此频率规模,感抗以20dB/dec添加,而ESR坚持常数,增益以-20dB/dec斜率下降。 幅频特性由-40dB/dec转为-20dB/dec斜率点为fesr,这里电容阻抗等于ESR。ESR供给一个零点。改动是渐近的,但所示的遽然改动也足够准确。

下一篇:开关电源的处理芯片介绍